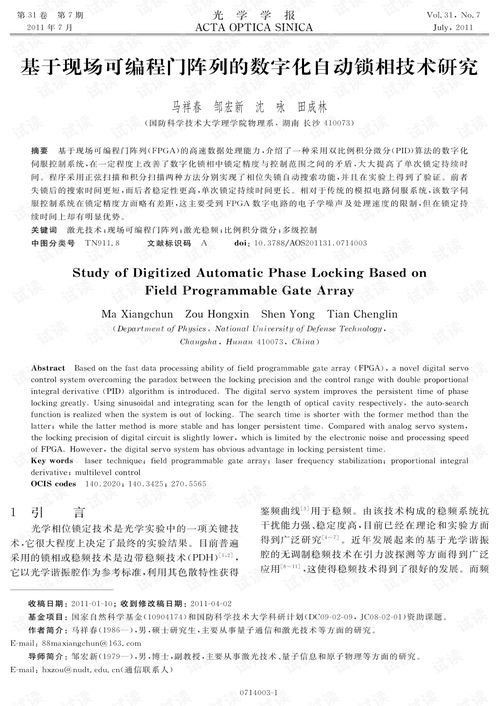

本文旨在探讨基于现场可编程门阵列的数字化自动锁相技术,分析其设计原理、系统架构、实现方法及其在通信、测量、电力电子等领域的应用优势与发展前景。

随着数字信号处理技术的飞速发展,传统的模拟锁相环因其存在温漂、元件老化、调试复杂等固有缺陷,已难以满足现代高精度、高稳定性电子系统的需求。数字化自动锁相技术应运而生,它利用数字电路或数字信号处理器实现对信号相位和频率的精确跟踪与同步。现场可编程门阵列作为一种高度灵活、可重构的半导体器件,凭借其并行处理能力强、开发周期短、易于实现复杂算法和系统集成等优势,成为实现高性能数字化锁相系统的理想硬件平台。

一、数字化自动锁相技术的基本原理

数字化自动锁相环的核心功能模块包括:数字鉴相器、数字环路滤波器和数字控制振荡器。其工作原理与模拟锁相环类似,但信号处理均在数字域完成。

- 数字鉴相器:负责比较输入参考信号与反馈信号的相位差,并将此差值转换为数字误差信号。常用算法包括过零检测法、乘法鉴相法(如正交下变频结合反正切运算)等,能够精确提取相位误差。

- 数字环路滤波器:作为系统的控制核心,其作用是滤除鉴相器输出中的高频噪声和干扰,并确定系统的动态响应特性(如锁定速度、带宽、稳定性)。通常采用比例-积分结构,其参数可灵活配置以适应不同应用需求。

- 数字控制振荡器:根据环路滤波器输出的控制字,生成频率和相位可精确调整的本地信号。数控振荡器的实现方式多样,如直接数字频率合成技术,它能产生高分辨率、高稳定度的输出信号。

二、基于FPGA的系统设计与实现

FPGA为实现上述数字化模块提供了高效平台。其设计流程主要包括算法建模、硬件描述语言编码、功能仿真、综合与布局布线、板级调试等步骤。

- 系统架构:典型的基于FPGA的数字化锁相环系统通常包含高速模数转换器、FPGA核心处理单元以及必要的存储器与外设接口。ADC将模拟输入信号数字化后送入FPGA处理。

- 模块实现:

- 鉴相器:可利用FPGA内部的乘法器、查找表和状态机资源高效实现。对于正交鉴相,可结合坐标旋转数字计算机算法进行相位差计算。

- 环路滤波器:可采用流水线或并行结构实现数字滤波器(如IIR或FIR滤波器),其系数可通过在线更新以适应动态变化。

- 数控振荡器:利用FPGA查找表实现相位累加器和正弦/余弦波形查找表,是构建高性能DDS的常用方法。

- 关键技术:

- 并行处理与流水线:FPGA的并行架构允许同时处理多个数据流,显著提升系统处理速度和实时性。

- 资源优化:通过合理设计数据位宽、采用时分复用或共享逻辑资源,在保证性能的同时优化FPGA的逻辑和存储资源消耗。

- 动态重配置:部分FPGA支持动态部分重配置,可在系统运行中切换锁相环参数或算法,实现多功能自适应。

三、技术优势与应用

基于FPGA的数字化自动锁相技术具有显著优势:

- 高精度与稳定性:数字处理避免了模拟器件的漂移,算法精度仅受限于字长和时钟频率,具有优异的长期稳定性。

- 灵活性与可重构性:锁相环的环路带宽、阻尼系数等参数可通过软件灵活调整,甚至算法结构也可重构,无需更改硬件。

- 易于集成与测试:整个锁相环系统可集成于单颗FPGA芯片中,与数字信号处理、通信协议处理等其他功能模块无缝集成,便于系统级设计与调试。

- 快速锁定与强抗干扰能力:通过优化数字环路滤波器算法,可以实现快速锁定,并结合数字滤波技术有效抑制特定频段的干扰。

其应用领域广泛:

- 通信系统:用于载波同步、时钟恢复、调制解调等,是软件无线电和认知无线电的关键技术。

- 电力电子:应用于并网逆变器、有源电力滤波器的电网同步,实现单位功率因数运行。

- 精密测量:在激光测距、原子钟同步、矢量网络分析仪等仪器中,用于产生高稳定度的本振信号或进行相位精确测量。

- 电机控制:用于无位置传感器电机控制中的转子位置与速度估算。

四、挑战与展望

尽管优势明显,该技术也面临一些挑战,如高速高精度ADC与FPGA接口设计、数字量化噪声与时钟抖动的抑制、复杂算法的实时实现与资源平衡等。随着FPGA工艺的不断进步(如更小的制程、更快的SerDes接口、集成硬核处理器),以及高级综合工具和基于模型的设计方法的发展,基于FPGA的数字化自动锁相技术将向着更高性能、更低功耗、更智能(如结合人工智能算法进行参数自适应优化)和更易用的方向发展,在5G/6G通信、新能源发电、工业物联网、航空航天等前沿领域发挥更为关键的作用。

基于现场可编程门阵列的数字化自动锁相技术,融合了数字信号处理的灵活性与FPGA硬件的高效性,是实现高可靠、高性能相位同步与频率合成的重要解决方案,具有深厚的理论研究价值和广阔的工程应用前景。